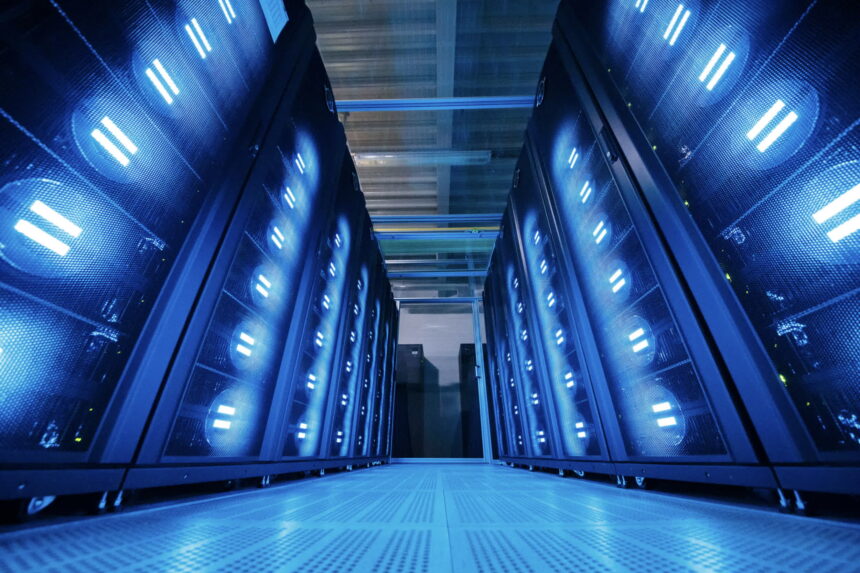

Tick tick tick: SiPearl is the French company selected by the European supercomputer consortium (EuroHPC JU) to develop a chip for the first exascale-class supercomputer in the region. The organization recently released updated specifications for the Rhea1 microchip, indicating that the first samples will be available later than initially expected.

While attending the ISC trade show in Hamburg, SiPearl shared the latest specifications and main features of the supercomputer chip Rhea1. This “first-generation” processor will utilize the Arm Neoverse V1 platform, empowering the high-performance computing tasks of Europe’s next-generation supercomputers while consuming less energy than competing products.

Previously, Rhea1’s specifications included 72 Neoverse V1 cores. However, SiPearl now indicates that the chip will feature a total of 80 Arm cores. The Rhea1 project always intended to incorporate 80 computing cores, the company clarified, with each core containing two 256-bit scalable vector extensions for “fast vector computations” in HPC scenarios.

The updated design includes built-in, high-bandwidth memory chips with four different HBM stacks per chip. Many HPC tasks, especially AI inferencing, will greatly benefit from integrated RAM. SiPearl is collaborating with Samsung to utilize HBM2e memory chips, although the Korean manufacturer will soon introduce the new HBM4 standard.

In addition to HBM, Rhea1 chips will also feature four DDR5 interfaces supporting two additional DIMM modules per channel. The design accommodates a total of 104 PCIe Gen5 lanes, with configurations of up to six x16 lanes plus two x4 lanes. The Neoverse technology also incorporates a specific Network-on-Chip component, the CMN-700 Coherent Mesh NoC, to facilitate rapid data sharing between compute and I/O elements.

Rhea1 is already supported by a wide range of compilers, libraries, and tools. It is capable of powering both “traditional” HPC workloads and newer AI inference tasks. According to the French company, the chip’s “generous” memory capacity will be the key element in delivering increased performance levels while retaining the energy-efficiency features of the Arm architecture, resulting in an unprecedented byte-per-FLOP ratio.

What SiPearl failed to emphasize, however, is that the Rhea project was initially intended to produce the first actual chips by 2022. The silicon company previously announced that the chips would be manufactured by TSMC in 2023 but is postponing Rhea1’s debut to 2025. Installation of Jupiter, Europe’s first exascale supercomputer designed around Rhea’s chip architecture, is expected to start this year.